# A Novel Low Line Regulation CMOS Voltage Reference Without BJTs and Resistors

Changqing Zhang, Xia Wu, Wanling Deng, and Junkai Huang

Abstract-A novel CMOS-only low line regulation voltage reference is presented in this paper. An output subcircuit composed of MOSFETs operating in the subthreshold region and saturation region is utilized to eliminate the temperature dependence of mobility and oxide capacitance, and produces a temperature-insensitive voltage reference. No bipolar junction transistors (BJTs) or resistors are used which can decrease the area greatly. By using most of the transistors operating in the subthreshold region, the power dissipation and the supply voltage are reduced. The proposed voltage reference is designed in the standard 0.18 µm CMOS process. The simulation results show that the output voltage is 958.971 mV at TT process corners, a temperature coefficient of 18.6096 ppm/°C range from -20 °C to 110 °C is achieved, the line regulator (LR) of the proposed circuit is 0.037 mV/V from 1.5 V to 2.5 V supply voltage, and the power supply rejection ratio (PSRR) is -75.77 dB at 100 Hz. The active area of the presented voltage reference is 0.0038 mm<sup>2</sup>.

*Keywords*—voltage reference, resistors, temperature coefficient, LR, PSRR.

### I. INTRODUCTION

Voltage reference (VR) circuit is an indispensable unit module in integrated circuit, and is used to provide a stable direct current (DC) reference, which is hardly affected by temperature drift, process variation and voltage fluctuation. Therefore, high precision references with low sensitivity to temperature, process, and supply voltage variations play an important role in many applications, such as analog-to-digital converters (ADC), digital-to-analog converters (DAC), phaselocked loops (PLL), oscillators (OSC), linear voltage regulators, memory and power management chips etc. [1]-[5].

Traditional bandgap reference (BGR) [6]-[8] is implemented by adding two voltages or currents with opposite temperature characteristics, thus producing a voltage independent of absolute temperature. In this method, the base-emitter voltage ( $V_{BE}$ ) of bipolar junction transistors (BJTs) is usually used to generate a negative temperature coefficient (TC) voltage, and the positive TC voltage is generated by using resistors and thermal voltage ( $V_T$ ). As  $V_{EB}$  is not a linear function of temperature, the voltage with low TC cannot be achieved without first or high order temperature compensation [9]. In order to solve this problem, a large number of compensation circuits are proposed, such as logarithmic-curvature compensation circuit, piecewise liner compensation circuits, etc. [10]-[11]. Although this method can compensate the TC of these circuit well, the use of these BJTs and resistors will occupy a large area, and will also require a high supply voltage and a complex compensation circuit.

Based on such problems, the CMOS VRs without BJTs have been proposed in [12]-[13]. In [12], the mutual temperature compensation principle of the threshold voltage of NMOS and PMOS transistors is utilized to obtain temperature-insensitive VR. In [13], the body bias compensation is employed, and its TC and LR are 48 ppm/°C and 3.4 mV/V respectively. In addition, the voltage reference composed of MOSFETs-only is also proposed in [14]-[15]. In [14], a curvature-compensation method is used to cancel logarithmic temperature dependence of mobility in the circuit, where the TC can be reduced to 7 ppm/°C and the PSRR achieves -43 dB. In [15], the design of VR uses the principle of the theramal compensation of a series composite NMOSTs to obtain reference output voltage whose LR can reach 2.217 mV/V and the TC can be reduced to 19.302 ppm/°C. All of these studies can compensate the TC well, and the BJT or resistor is not introduced in the circuit. However, some new issues such as high LR and low PSRR may follow.

In this paper, we propose a novel CMOS VR. It should be noted that there are no BJTs or resistors used in the circuit. By the use of the transistors operating in the subthreshold region and a MOS resistor operating in the triode region, the area of the proposed VR can be greatly decreased. Since the current source subcircuit uses the feedback technique, the amplifier is omitted, the line regulator (LR) is improved, and the power supply rejection ratio (PSRR) achieves -75.77 dB. The temperature compensation is obtained by using the output subcircuit which is composed of MOSFETs operating in the subthreshold region and saturation region, and it adjusts the output voltage. The proposed design achieves less temperature sensitivity and a smaller line sensitivity. Therefore, the voltage reference can be used in Comparators, A/D and D/A converters, DC-DC converters, and PLLs and so on. The voltage reference can be applied to mini-computers, wearable electronic devices, wireless sensors, smart phones etc. The working principle of this circuit, simulation verification, and other details will be discussed in the following sections.

## II. PRINCIPLE AND ARCHITECTURE OF PROPOSED VR

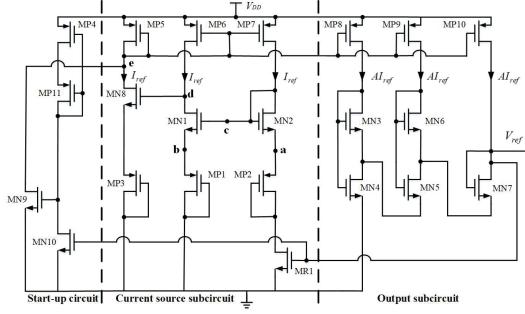

The principle of our voltage reference is illustrated in Fig. 1.

510630, China. Corresponding author is Junkai Huang (e-mail: hjk196310@126.com), Changqing Zhang (e-mail: 463971191@qq.com), Xia Wu (e-mail: 726558441@qq.com), Wanling Deng (e-mail: dwanl@126.com).

This work was supported by the Guangdong Natural Science Foundation under Grant 2020A1515010567. C. Zhang, X. Wu, W. Deng, and J. Huang are with the Department of Electronic Engineering, Jinan University, Guangzhou

The circuit consists of start-up circuit, current source subcircuit, and output subcircuit. The current source subcircuit uses a MOS resistor MR1 operating in strong-inversion and deep-triode regions instead of ordinary resistors. It generates the current  $I_{ref}$ . The output subcircuit accepts current  $I_{ref}$  though PMOS current mirrors operating in the saturation region and produces an output voltage (i.e., reference voltage),  $V_{ref}$ . All the MOSFETs except for MR1, MN4, MN5, MN7, and PMOS current mirror are operated in the subthreshold region. The circuit generates two voltages with a negative temperature coefficient (TC) and a positive TC. Then, it adds them together to produce a constant voltage with a zero TC. The operation and design considerations of each block will be discussed in the following sections.

# A. Principle of temperature compensation

The current source subcircuit is illustrated in the middle of Fig. 1. All the MOSFETs except for MP5 - MP7 and MR1 are operated in the subthreshold region. The subthreshold drain current  $I_D$  of a MOSFET is a function of temperature. If the source-drain voltage  $V_{DS}$  satisfices  $V_{DS} \ge 4V_T$  [16], it can be written as

$$I_D = \mu C_{OX} (\delta - 1) K V_T^2 e^{\left(\frac{V_{GS} - V_{TH}}{\delta V_T}\right)}$$

(1)

where  $\mu$  is the temperature-dependent carrier mobility as  $\mu(T) = \mu_0(T/T_0)^{-m}$  [17], *m* is a constant about 1.5-2,  $C_{OX}$  is the oxide capacitance per unit area,  $\delta$  is the subthreshold slope factor, *K* is the transistor aspect ratio as K=W/L,  $V_T$  is the thermal voltage and  $V_T=K_BT/q$ ,  $K_B$  is the Boltzmann constant, *q* is the elementary charge,  $V_{DS}$  is the drain-source voltage,  $V_{TH}$  is the threshold voltage, and  $V_{GS}$  is the gate-source voltage.

The structure of negative feedback loop introduced by MP3, MN8, MP5, MP7, MN2 and MN1 is shown in the current

source subcircuit of Fig. 1. Due to the negative feedback, the voltage of node c is stable. Therefore gate-source voltage  $V_{SG(MP1)}$  in MP1 is equal to the sum of gate-source voltage  $V_{SG(MP2)}$  in MP2 and drain-source voltage  $V_{DS(MR1)}$  in MR1, i.e.,

$$V_{SG(MP1)} = V_{SG(MP2)} + V_{DS(MR1)}$$

(2)

here,  $V_{SG(MP1)}$  and  $V_{SG(MP2)}$  are the gate-source voltages of MP1 and MP2, respectively.  $V_{DS(MR1)}$  is the drain-source voltage of MR1. All symbols in subscript brackets correspond to transistors. Substituting (2) into (3), we can get the expression, i.e.,

$$V_{DS(MR1)} = \delta V_T ln\left(\frac{K_{(MP2)}}{K_{(MP1)}}\right)$$

(3)

MOS resistor  $R_{MRI}$  are operated in a strong-inversion, deeptriode region, so its resistance  $R_{MRI}$  is given by

$$R_{MR1} = \frac{1}{K_{(MR1)}\mu_n C_{OX}(V_{ref} - V_{TH(MR1)})}$$

(4)

Using (2), (3), and (4), the bias current  $I_{ref}$  of MP7 can be derived as

$$I_{ref} = \kappa_{(MR_1)} \mu_n c_{OX} (v_{ref} - v_{TH(MR_1)}) \delta V_T ln \left(\frac{K_{(MP_2)}}{K_{(MP_1)}}\right)$$

(5)

In the output subcircuit, all the MOSFETs except for MN3 and MN6 are operated in the saturation region, and MN3 and MN6 are operated in the subthreshold region. For  $I_{ref}$ , the gate-source voltages of transistors MN3 to MN7 form a closed loop, and the currents of MN4, MN5 are respectively denoted as  $3AI_{ref}$  and  $2AI_{ref}$ , where  $A = K_{MP8}/K_{MP7}$ . We find that output voltage  $V_{ref}$  of the circuit is given by

$$V_{ref} = V_{GS(MN4)} - V_{GS(MN3)} + V_{GS(MN5)} - V_{GS(MN6)} + V_{GS(MN7)}$$

(6)

The I-V characteristic of an n-MOSFET operating in the saturation region can be approximated by [18]

$$V_D = \frac{1}{2} \mu C_{OX} K (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(7)

1

Fig. 1. Schematic of the proposed voltage reference.

where  $\lambda$  is the channel length modulation coefficient. This designed circuit use long channel device to suppress the effect of channel length modulation. Substituting (1), (5) and (7) into (6), the  $V_{ref}$  can be rewritten as

$$V_{ref} = V_{TH} + \left(\sqrt{\frac{2A}{K_{(MN7)}}} + \sqrt{\frac{4A}{K_{(MN5)}}} + \sqrt{\frac{6A}{K_{(MN4)}}}\right) * \sqrt{K_{(MR1)}(V_{ref} - V_{TH})\delta V_T ln\left(\frac{K_{(MP2)}}{K_{(MP1)}}\right)} - \delta V_T ln\left(\frac{AK_{(MR1)}(V_{GS(MR1)} - V_{TH})\delta ln\left(\frac{K_{(MP2)}}{K_{(MP1)}}\right)}{(\delta^{-1})K_{(MN)}V_T}\right) - \delta V_T ln\left(\frac{AK_{(MR1)}(V_{GS(MR1)} - V_{TH})\delta ln\left(\frac{K_{(MP2)}}{K_{(MP1)}}\right)}{(\delta^{-1})K_{(MN3)}V_T}\right)$$

(8)

where we assumed that the mismatch between the threshold voltages of the transistors can be ignored. Besides, the temperature dependence of the threshold voltage can be given by

$$V_{TH} = V_{TH0} - \alpha T \tag{9}$$

where  $V_{TH0}$  is the threshold voltage at 0 K,  $\alpha$  is TC of  $V_{TH}$  [11]. Substituting (9) into (8), the  $V_{ref}$  can be given by

$$V_{ref} = \left(\sqrt{\frac{2A}{K_{(MN7)}}} + \sqrt{\frac{4A}{K_{(MN5)}}} + \sqrt{\frac{6A}{K_{(MN4)}}}\right) *$$

$$\sqrt{K_{(MR1)} \left(V_{ref} - V_{TH} + \alpha T\right) \delta V_T ln \left(\frac{K_{(MP)}}{K_{(MP1)}}\right)}$$

$$-2\delta V_T ln \left(\frac{AK_{(MR1)} \left(V_{ref} - V_{TH0} + \alpha T\right) \delta ln \left(\frac{K_{(MP)}}{K_{(MP)}}\right)}{(\delta^{-1}) V_T}\right)$$

$$(10)$$

$$+\delta V_T ln(K_{(MN6)}K_{(MN3)}) + V_{TH0} - \alpha T$$

In this designed circuit, when the TC has the smallest value, the relation of  $V_{ref} - V_{TH0} \ll KT$  can be developed [19]. As a result,  $V_{ref}$  can be rewritten as

$$V_{ref} = V_{TH0} + \left(\frac{\delta K_B ln(K_{(MN6)}K_{(MN3)})}{q} + B - \alpha\right)T - \frac{2\delta K_B}{q}ln\left(\frac{AK_{(MR)}q\delta \alpha ln\left(\frac{K_{(MP)}}{K_{(MP1)}}\right)}{(\delta - 1)K_B}\right)T$$

(11)

where

$$B = \left(\sqrt{\frac{2A}{K_{(MN)}}} + \sqrt{\frac{4A}{K_{(MN)}}} + \sqrt{\frac{6A}{K_{(MN4)}}}\right) * \\ \sqrt{\frac{K_{(MR)}\alpha\delta K_B ln\left(\frac{K_{(MP)}}{K_{(MP1)}}\right)}{q}}.$$

According to (11), a zero TC voltage can be obtained by choosing a proper  $k_{(i)}$  on condition that

$$\frac{\delta K_B ln(K_{(MN6)}K_{(MN3)})}{q} + B - \alpha - \frac{2\delta K_B ln(\frac{AK_{(MR1)}q\delta \alpha ln(\frac{K_{(MP)}}{K_{(MP1)}})}{(\delta - 1)K_B})}{q} = 0$$

(12)

Therefore, we can get a high-precision voltage reference based on the above temperature compensation principle.

# B. Negative feedback analysis

The channel length modulation effect causes variation of the output voltage and the bias current when the supply voltage varies [20]. The LR performance is a DC parameter, which

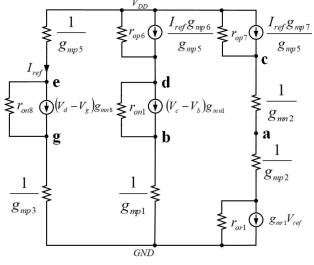

represents the variation of output voltage caused by the input supply change. On the other hand, PSRR is defined as PSRR =  $20lg(\Delta V_{ref}/\Delta V_{DD})$ . It is not only the complement of supply gain but it also includes the entire frequency spectrum. Therefore, A voltage reference that is insensitive to the supply voltage is very important. In Fig. 1, a negative feedback loop composed of MP3, MN8, MP5, MP7, MN2 and MN1 is introduced to improve the performances of PSRR and LR. If the voltage  $V_d$  of the node d rises with the supply voltage variation,  $V_e$  would drop, and  $V_c$  would rise. Since the gain of the negative feedback loop is greater than the positive feedback loop gain introduced by MN1, MN8, MP5 and MP6, V<sub>d</sub> would fall at last. In addition, MP1-MP3 working in the subthreshold region are diode connected, and their  $V_{DS}$  voltages are much larger than  $4V_T$ , so they are almost constant for the small variation of bias current. Fig. 2 shows the small signal model of the current source subcircuit at low frequencies.

Fig. 2. Small-signal model of the current source subcircuit.

$$I_{ref} = (V_{DD} - V_e)g_{mp5}$$

(13)

$$I_{ref} = \frac{V_e - V_g}{r_{on8}} + (V_d - V_g)g_{mn8} = V_g g_{mp3}$$

(14)

$$(V_{DD} - V_e)g_{mp6} + \frac{V_{DD} - V_d}{r_{op6}} = \frac{V_d - V_b}{r_{on1}} + (V_c - V_b)g_{mn1}$$

=  $V_b g_{mp1}$  (15)

$$(V_{DD} - V_e)g_{mp7} + \frac{(V_{DD} - V_c)}{r_{op7}} = (V_c - V_a)g_{mn2}$$

(16)

$$V_a = [(V_c - V_a)g_{mn2} - V_{ref}g_{mr1}]r_{or1} + (V_c - V_a)\frac{g_{mn2}}{g_{mn2}}$$

(17)

Herein,  $g_{mni}$  and  $g_{mpi}$  represent the transconductances of MNi and MPi, respectively. The output resistances of MPi and MNi are marked as  $r_{opi}$  and  $r_{oni}$ , respectively.  $V_{DD}$  is the supply voltage. Through (13)-(17), we can get the expression. i.e.,

$$V_{ref} = \frac{V_g}{g_{mr1}} \left( \frac{g_{mp3} g_{mp7}}{g_{mp5}} - \frac{A}{r_{op7}} \right) + \frac{V_{DD}}{g_{mr1} r_{op7}}$$

(18)

where

$$A = \frac{g_{mn1} + g_{mp1}}{g_{mp1}g_{mn1}} \left( \frac{g_{mp3}g_{mp6}}{g_{mp5}} \frac{g_{mp3} + g_{mn8}}{g_{mn8}r_{op6}} \right) - \frac{g_{mn8} + g_{mp3}}{r_{on1}g_{mn8}g_{mn1}}$$

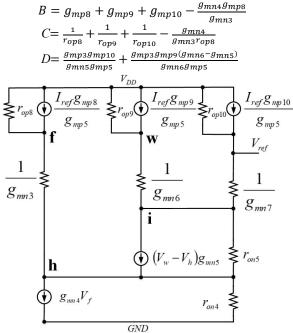

Fig. 3 shows the small signal model of the output subcirc

Fig. 3 shows the small signal model of the output subcircuit. Similarly, we can get the following expressions:  $V_{DD} - V_f$  (10)

$$\frac{DD - V_f}{r_{op8}} + (V_{DD} - V_e)g_{mp8} = (V_f - V_h)g_{mn3}$$

(19)

$$\frac{V_{DD} - V_w}{r_{op9}} + (V_{DD} - V_e)g_{mp9} = (V_w - V_i)g_{mn6}$$

(20)

$$\frac{V_{DD} - V_{ref}}{r_{op10}} + (V_{DD} - V_e)g_{mp10} = (V_{ref} - V_i)g_{mn7}$$

(21)

$$(V_w - V_i)g_{mn6} + (V_{ref} - V_i)g_{mn7} = \frac{V_i - V_h}{r_{on5}}$$

(22)

+(V\_w - V\_h)g\_{mn5}

$$(V_f - V_h)g_{mn3} + (V_w - V_i)g_{mn6} + (V_{ref} - V_i)g_{mn7}$$

$$= \frac{V_h}{r_{ref}} + V_f g_{mn4}$$

(23)

Through (19)-(23), we can get

$$V_{ref} = V_g \left( \frac{g_{mp3}g_{mp10}}{g_{mn7}g_{mp5}} + \frac{\frac{g_{mp3}}{g_{mp5}g_{mn4}}B + D}{\frac{g_{mn6}}{g_{mn5}}g_{mn5} - g_{mn6}} \right) + V_{DD} *$$

$$\left( \frac{1}{g_{mn7}r_{op10}} + \frac{c}{g_{mn4}} - \frac{1}{g_{mn5}r_{op10}} - \frac{g_{mn6} - g_{mn5}}{g_{mn6}r_{op5}} \right)$$

(24)

where

Fig. 3. Small-signal outputt subcircuit.

Using (18) and (24),

$$V_{ref}/V_{DD}$$

can be written as

$$\frac{V_{ref}}{V_{DD}} = \frac{E - \left(\frac{g_{mp3}g_{mp7}r_{op7}}{g_{mp5}} - A\right)F}{\frac{g_{mp3}g_{mp7}r_{op7}}{g_{mp5}} - A - g_{mr1}r_{op7}E}$$

(25)

where

$$E = \left(\frac{g_{mp3}g_{mp10}}{g_{mn7}g_{mp5}} + \frac{g_{mp3}g_{mn4}}{g_{mp5}g_{mn4}}B + D}{g_{mp5}g_{mn5}}\right)$$

$$F = \frac{1}{g_{mn7}r_{op10}} + \frac{c}{g_{mn4}} - \frac{1}{g_{mn5}r_{op10}} - \frac{g_{mn6}-g_{mn5}}{g_{mn6}r_{op9}}$$

From (25), we can deduce that the sensitivity of  $V_{ref}$  to  $V_{DD}$  is proportional to  $g_{mp3}/g_{mp5}$ ,  $g_{mr1}$ , and  $g_{mp8}$ . By adjusting the transistor aspect ratio of MP9, MN5, MN6, etc., the LR can be further improved. Therefore, the VR independent of  $V_{DD}$  can be obtained by reasonably adjusting the aspect ratio of MPi and MNi.

## III. SIMULATION RESULTS AND DISCUSSION

In order to verify the performance of the proposed VR, a series of simulation results have been implemented under the TSMC 0.18  $\mu$ m CMOS process.

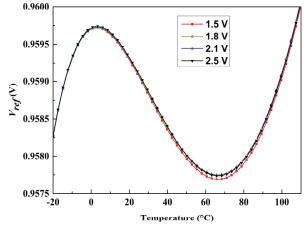

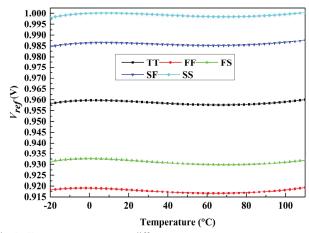

Fig. 4. *V<sub>ref</sub>* versus temperature at different supply voltages.

Fig. 4 shows the simulation results of the output voltage  $V_{ref}$  versus temperature at various supply voltages. When the supply voltage varies from 1.5 V to 2.5 V, the minimum and maximum values of  $V_{ref}$  in the range from -20 to 110 °C are 958.971 mV and 959.008 mV, respectively. Under four different supplied voltages, the average value of TC is about 18.6893 ppm/°C, and the maximum deviation of the temperature coefficient is 0.1598 ppm/°C.

Fig. 5. Vref versus temperature at different process corners.

The Vref of the proposed circuit versus temperature at

different process corners is shown in Fig. 5, where the best case occurs at the SS process corner whose TC is 18.2362 ppm/°C, while the worst case occurs at the FS process corner whose TC is 23.3690 ppm/°C, and the difference between them is 5.1328 ppm/°C. This simulation result is consistent with the derivations of (10) to (12). Therefore, under different supply voltages and process corners, the output voltage  $V_{ref}$  has a stable TC.

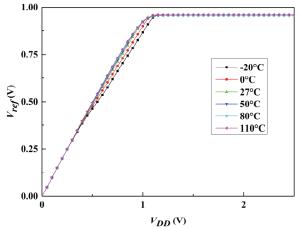

Fig. 6 shows that  $V_{ref}$  varies with  $V_{DD}$  at different temperatures. Obviously, curves with different temperatures have similar trends and due to the proposed circuit structure, the circuit begins to output the stable  $V_{ref}$  after  $V_{DD} = 1.5$  V.

Fig. 6. Vref versus VDD at different temperatures.

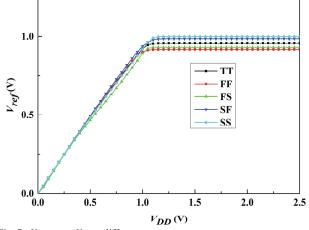

Fig. 7. V<sub>ref</sub> versus V<sub>DD</sub> at different process corners.

Fig. 7 shows that  $V_{ref}$  varies with  $V_{DD}$  at different process corners when the supply voltage is 1.5 V. It is clearly that the output voltage is almost constant when the supply voltage is greater than 1.5 V, and all the transistors work in their corresponding regions. Under the TT corner, when the supply voltage sweeping from 1.5 V to 2.5 V,  $V_{ref}$  changes from 959.971 mV to 959.008 mV. Consequently, the LR can be calculated to be 0.037 mV/V. The best and worst LR are 0.025 mV/V and 0.053 mV/V in FS and SF corners, respectively. Thence, it can be seen that this output voltage is not affected by power supply voltage and temperature changes. This result is consistent with the derivation of (25). The low LR can be achieved due to the negative feedback structure, which improves the performance of the proposed circuit.

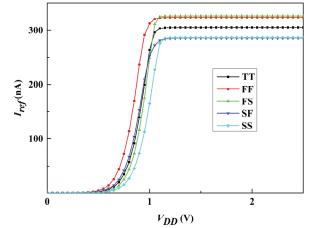

Fig. 8.  $I_{ref}$  versus  $V_{DD}$  at different process corners.

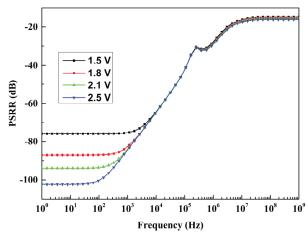

Fig. 9. PSRR versus frequency at different power supplies.

|                                      |                                  |                   | IADLLI               |                       |          |         |

|--------------------------------------|----------------------------------|-------------------|----------------------|-----------------------|----------|---------|

|                                      | S                                | UMMARY OF CRITICA | AL PARAMETERS AT FIV | 'E KINDS OF PROCESS O | CORNERS. |         |

| corners                              |                                  | TT                | FF                   | FS                    | SF       | SS      |

| TC (ppm/°C) @ V <sub>DD</sub> =1.5 V |                                  | 18.6096           | 22.5417              | 23.3690               | 22.3891  | 18.2362 |

| PSRR (dB)                            | 100 Hz<br>V <sub>DD</sub> =1.5 V | -75.77            | 75.08                | -88.69                | -70.46   | -79.18  |

| LR (mV/V)                            |                                  | 0.037             | 0.037                | 0.025                 | 0.053    | 0.031   |

| $V_{ref}$ (mV) @ $V_{DD}$ =1.5 V     |                                  | 958.971           | 917.955              | 931.540               | 986.055  | 999.698 |

TABLE I

The simulation curve of the bias current  $I_{ref}$  versus  $V_{DD}$  at different process corners is presented in Fig. 8. It is worth noting that for all the process corners, the supply current is almost constant in the range from 1.5 V to 2.5 V. Under TT corner, the offset of this current  $I_{ref}$  is only 60 pA when the supply voltage changes 1.5 V, and the minimum and maximum deviation values of  $I_{ref}$  in the five corners are 52 pA and 70 pA, respectively. The current is almost independent of the supply voltage. Moreover, when the power supply voltage is 1.5 V, the total current consumed by this circuit at the TT corner is 3.77  $\mu$ A.

Fig. 9 shows that PSRR varies with frequency at four different  $V_{DD}$  cases. From the picture, when  $V_{DD}$  is 2.5 V, the PSRR achieves -100.3 dB at 100 Hz. Under the condition of  $V_{DD} = 1.5$  V, the PSRR of the proposed VR is around -75.77 dB at 100 Hz.

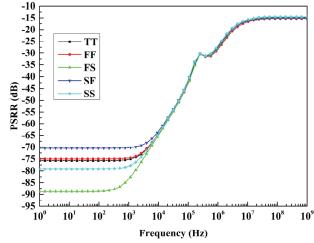

Fig. 10. PSRR versus frequency at different process corners.

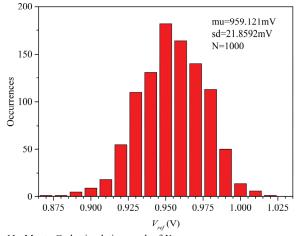

Fig. 11. Monte-Carlo simulation result of Vref.

Fig. 10 illustrates the simulation curves of PSRR versus frequency at different process corners when the supply voltage is 1.5 V. When the frequency is 100 Hz, the best and worst PSRR are -88.69 dB and -70.46 dB in FS and SF corners, respectively. Through the negative feedback technique, the variation of  $I_{ref}$  is very small (see Fig. 8), the PSRR performance also benefits from this negative feedback structure.

The sensitivity of the output reference voltage is evaluated by Monte Carlo simulation 1000 runs, which takes into account the effects of the mismatch and process variations in all the transistors of the proposed reference. When  $V_{DD}$  is 1.5 V, Monte-Carlo simulation result of  $V_{ref}$  at 27 °C is shown in Fig. 11. It can be clearly observed that the average value of  $V_{ref}$  is 959.121 mV, the standard deviation is 21.8592 mV, and the coefficient of variation  $\sigma/\mu$  is about 2.27%.

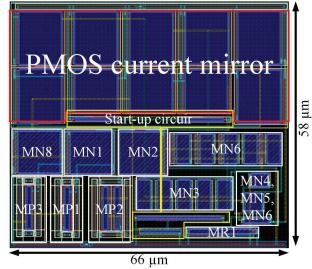

From (12), we can see that TC of the proposed reference can become smaller by increasing  $K_{(MN3)}$  and  $K_{(MN6)}$  or decreasing  $K_{(MN4)}$ ,  $K_{(MN5)}$  and  $K_{(MN7)}$ . Besides, the PMOS current mirror uses the same large size transistors to reduce current mismatch and channel length modulation effects. As shown in Fig. 12, the PMOS current mirror occupies a large area in the layout. However, the VR circuit proposed in this paper is simple in structure and without using resistors and BJTs. Therefore, the final total layout area is only 0.0038 mm<sup>2</sup> (66 µm \* 58 µm).

Fig. 12. Layout of the proposed VR.

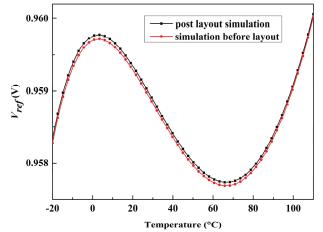

Fig.13. Comparison between simulation and post layout simulation at TT corner.

The comparison of output voltage  $V_{ref}$  as a function of temperature between simulation and post layout simulation is shown Fig. 13. From the picture, we can know that the results

| COMPARISONS AMONG THE PROPOSED CIRCUIT AND OTHER VOLTAGE REFERENCE CIRCUITS. |           |          |                |         |         |             |  |  |  |  |

|------------------------------------------------------------------------------|-----------|----------|----------------|---------|---------|-------------|--|--|--|--|

| Parameter                                                                    | This work | [11]     | [12]           | [13]    | [14]    | [15]        |  |  |  |  |

| Process (µm)                                                                 | 0.18      | 0.18     | 0.35           | 0.13    | 0.065   | 0.18        |  |  |  |  |

| BJTs                                                                         | None      | None     | None           | None    | None    | None        |  |  |  |  |

| Resistors                                                                    | None      | Yes      | Yes            | None    | None    | None        |  |  |  |  |

| Temperature                                                                  | -20-110   | -20-80   | 0-130          | 0-100   | -40-125 | -40-85      |  |  |  |  |

| range (°C)                                                                   |           |          |                |         |         |             |  |  |  |  |

| Supply voltage                                                               | 1.5-2.5   | 1.35-1.8 | 1.8/3/4.5      | 1.2-2.3 | 1.2-2.0 | 1.25-2.0    |  |  |  |  |

| (V)                                                                          |           |          |                |         |         |             |  |  |  |  |

| $V_{ref}$ (mV)                                                               | 958.971   | 630      | 847.5          | 781     | 594.5   | 536.01      |  |  |  |  |

| TC (ppm/°C)                                                                  | 18.6096   | 14.1     | 13.6/11.8/12.7 | 48      | 7       | 19.302      |  |  |  |  |

| LR(mV/V)                                                                     | 0.037     | 0.298    | 0.185          | 2.6554  | 0.076   | 2.217       |  |  |  |  |

| PSRR (dB)                                                                    | -75.77    | -75.7    | -72            | -51.4   | -43     | -51.4@10 Hz |  |  |  |  |

| @100Hz                                                                       | @1.5 V    | @1.6 V   | @3.0 V         | @1.2 V  | @ 1.2 V | Ň/A         |  |  |  |  |

| Area (mm <sup>2</sup> )                                                      | 0.0038    | 0.015    | 0.014          | 0.014   | 0.03    | 0.0077      |  |  |  |  |

TABLE II

of the simulation and post layout simulation only have a maximum difference of 0.054 mV, Therefore, the design of the circuit is reasonable.

The critical technical performances of the proposed voltage reference at five different process corners are shown in details in Table I. Under these five process corners, the worst TC, PSRR, LR are 23.3690 ppm/°C, -70.46 dB, 0.053 mV/V respectively. In addition, the maximum deviation of each performance is also very small. Therefore, the proposed circuit meets the design requirements. The characteristics of proposed circuit compared to other voltage reference circuits are shown in Table II where TC and PSRR of the proposed circuit are optimized, and the LR and area are significantly improved.

# IV. CONCLUSION

This paper proposes a novel low LR CMOS voltage reference without BJTs and resistors, which is area efficient and less sensitive to temperature. The design is achieved by the TSMC 0.18  $\mu$ m CMOS process. The output voltage with a low TC is obtained by utilizing output subcircuit composed of MOSFETs operating in the subthreshold region and saturation region. Through the use of the negative feedback technology, the amplifer is omitted, and the low LR can be realized. In the range of -20 to 110 °C, the proposed VR achieves TC of 18.6096 ppm/°C for a 1.5 V supply, while the PSRR is -75.77 dB at 100 Hz. The maximum variation of output voltage is only 0.037 mV from 1.5 V to 2.5 V supply voltage. The proposed VR with low TC, low LR, and high PSRR, can be attractive in high-precision systems.

#### REFERENCES

- [1] A. Bendali and Y. Audet, "A 1-V CMOS current reference with temperature and process compensation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 7, pp. 1424-1429, Jul. 2007, doi: 10.1109/TCSI.2007.900176.

- [2] A. Becker-Gomez, T. L. Viswanathan, and T. R. Viswanathan, "A lowsupply-voltage CMOS sub-bandgap reference," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 55, no. 7, pp. 609-613, Jul. 2008, doi: 10.1109/TCSII.2008.921580.

- [3] T. R. Perry, S. H. Lewis, A. P. Brokaw, and T. R. Viswanathan, "A 1.4 V supply CMOS fractional bandgap reference," *IEEE Journal of Solid-State*

*Circuits*, vol. 42, no. 10, pp. 2180-2186, Oct. 2007, doi: 10.1109/JSSC.2007.905236.

- [4] G. Bassi, L. Colalongo, A. Richelli, and Z. M. Kovacs-Vajna, "100 mV-1.2 V fully-integrated DC–DC converters for thermal energy harvesting," *IET Power Electronics*, vol. 6, no. 6, pp. 1151-1156, Feb. 2013, doi: 10.1049/iet-pel.2012.0625.

- [5] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "CMOS smart sensor for monitoring the quality of perishables," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 4, pp. 798-803, Apr. 2007. doi: 10.1109/JSSC.2007.891676.

- [6] K. E. Kuijk, "A precision reference voltage source," *IEEE Journal of Solid-State Circuits*, vol. 8, no. 3, pp. 222-226, Jun. 1973, doi: 10.1109/jssc.1973.1050378.

- [7] I. Lee, G. Kim, and W. Kim, "Exponential curvature compensated BiCMOS bandgap references," *IEEE Journal of Solid-State Circuits*, vol. 29, no. 11, Nov. 1994, doi: 10.1109/4.328634.

- [8] K. M. Tham and K. Nagaraj, "A low supply voltage high PSRR voltage reference in CMOS process," *IEEE Journal of Solid-State Circuits*, vol. 30, no. 5, May. 1995, pp. 586-590, doi: 10.1109/4.384173.

- [9] Y. H. Lam and W. H. Ki, "CMOS bandgap references with self-biased symmetrically matched current-voltage mirror and extension of sub-1-V design," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 18, no. 6, Jun. 2010, pp. 857-865, doi: 10.1109/TVLSI.2009.2016204.

- [10] Z. Y. Luo, Y. Lu, M. Huang, J. M. Jiang, S. W. Sin, U. Seng-Pan, and R. P. Martins, "A sub-1V 78-nA bandgap reference with curvature compensation," *Microel ectronics Journal*, vol. 63, May. 2017, pp. 35-40, doi: 10.1016/j.mejo.2017.02.016.

- [11] Z. K. Zhou, Y. Shi, C. Gou, X. Wang, G. Wu, J. F. Feng, Z. Wang, and B. Zhang "A resistorless low-power voltage reference," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 63, no. 7, Jul. 2016, pp. 613-617, doi: 10.1109/TCSII.2016.2530096.

- [12] Z. K. Zhou, P. S. Zhu, Y. Shi, H. Y. Wang, Y. Q. Ma, X. Z. Xu, L. Tan, X. Ming, and B. Zhang, "A CMOS voltage reference based on mutual compensation of V<sub>tn</sub> and V<sub>tp</sub>," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 59, no. 6, Jun. 2012, pp. 341-345, doi: 10.1109/TCSII.2012.2195065.

- [13] H. Luo, Y. Han, R. C. C. Cheung, G. Liang, and D. Zhu, "Subthreshold CMOS voltage reference circuit with body bias compensation for process variation," *IET circuits Devices & systems*, vol. 6, no. 3, May. 2012, pp. 198-203, doi: 10.1049/iet-cds.2011.0170.

- [14] T. N. Ghanavati, E. Farshidi, H. Sjoland, and A. Kosarian, "A high precision logarithmic-curvature compensated all CMOS voltage reference," *Analog integrated circuits and signal processing*, vol. 99, no. 2, pp. 383– 392, May. 2019, doi: 10.1007/s10470-018-1296-0.

- [15] S. S. Chouhan and K. Halonen, "Design and implementation of a micropower CMOS voltage reference circuit based on thermal compensation of V<sub>gs</sub>," *Microelectronics Journal*, vol. 46, no. 1, pp. 36-42, Jan. 2015, doi: 10.1016/j.mejo.2014.09.015.

- [16] Q. L. Li, W. L. Deng, X. Y. Ma and J. K. Huang, "A novel low line regulation voltage reference with no amplifier," *Journal of Circuits Systems and Computers*, vol. 27, no. 10, pp. 1850152, Sep. 2018, doi: 10.1142/S0218126618501529.

- [17] N. Alhassan, Z. Zhou, and E. S. Sanchez, "An all-MOSFET voltage reference with-50-dB PSR at 80 MHz for low-power SoC design," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 8, pp. 892-896, Aug. 2017, doi: 10.1109/TCSII.2016.2614527.

- [18] Y. T. Wang, Z. M. Zhu, J. J. Yao, and Y. T. Yang, "A 0.45-V, 14.6-nW CMOS subthreshold voltage reference with no resistors and no BJTs," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 62, no. 7, pp. 621-625, Jul. 2015, doi: 10.1109/TCSII.2015.2415292.

- [19] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "A 300 nW 15 ppm/degrees C, 20 ppm/ degrees C, 20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 7, pp. 2047-2054, Jul. 2009, doi: 10.1109/JSSC.2009.2021922.

- [20] Y. H. Zeng, Y. R. Huang, Y. L. Luo, and H. Z. Tan, "An ultra-low-power CMOS voltage reference generator based on body bias technique," *Microelectronics Journal*, vol. 44, no. 12, pp. 1145-1153, Dec. 2013, doi: 10.1016/j.mejo.2013.07.003.

**Changqing Zhang** received the B.A. degree from Hunan University of Science and Engineering, YongZhou, China, in 2017. He is currently pursuing the M.S. degree with Jinan University, Guangzhou, China. His current research interest includes the design of integrated circuit and system on chip.

**Wanling Deng** received the B.S. and Ph.D. degrees in electrical engineering from the South China University of Technology, Guangzhou, China, in 2003 and 2008, respectively. Since 2008, she has been an Associate Professor with the Department of Electronic Engineering, Jinan University, Guangzhou. Her current research interests include thinfilm transistor (TFT) devices and physics,

particularly poly-Si TFT and AOS TFT modeling.

Xia Wu received received the B.S. degree in electrical engineering from Jinan University, Guangzhou, China, in 1997 and the M.S. degree in education management from South China Normal University, Guangzhou, China, in 2009 respectively. Since 1997, she has worked in Jinan University. Her current research interests include semiconductor device physics and test methods.

Junkai Huang received the B.S. degree in applied physics and the M.S. degree in semiconductor device from Jinan University, Guangzhou, China, in 1985 and 1990, respectively, and the Ph.D. degree from the Institute of Microelectronics, South China University of Technology, Guangzhou, in 2011. He is currently a Professor with

Jinan University. His current research interests include thinfilm transistors' modeling, simulation, and integrated circuit design.